### www.ti.com

## SECONDARY SIDE AVERAGE CURRENT MODE CONTROLLER

#### **FEATURES**

- Practical Secondary Side Control of Isolated Power Supplies

- 1 MHz Operation

- Differential AC Switching Current Sensing

- Accurate Programmable Maximum Duty Cycle

- Multiple Chips Can be Synchronized to Fastest Oscillator

- Wide Gain Bandwidth Product (70 MHz, Acl >10) Current Error and Current Sense Amplifiers

- Up to Ten Devices Can Easily Share a Common Load

#### DESCRIPTION

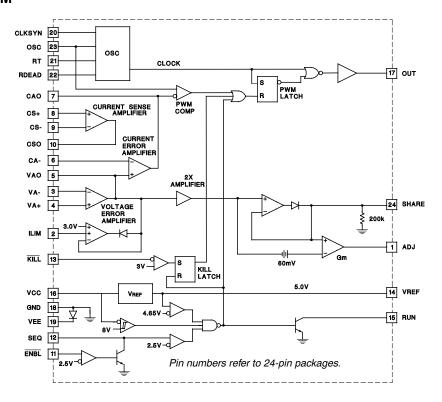

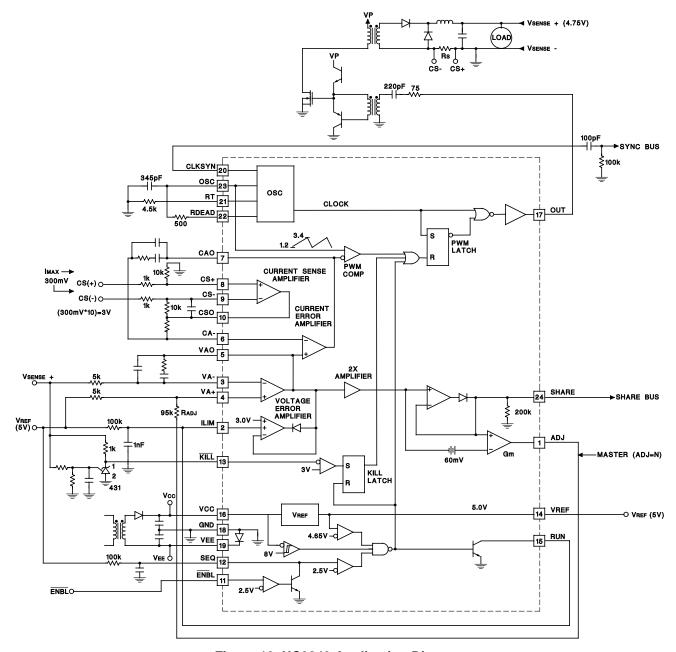

The UC3849 family of average current-mode controllers accurately accomplishes secondary side average current mode control. The secondary-side output voltage is regulated by sensing the output voltage and differentially sensing the ac switching current. The sensed output voltage drives a voltage error amplifier. The ac switching current, monitored by a current sense resistor, drives a high bandwidth, low offset current sense amplifier. The outputs of the voltage error amplifier and current sense amplifier differentially drive a high bandwidth, integrating current error amplifier. The sawtooth waveform at the current error amplifier output is the amplified and inverted inductor current sensed through the resistor. This inductor current down-slope compared to the PWM ramp achieves slope compensation, which gives an accurate and inherent fast transient response to changes in load.

#### **BLOCK DIAGRAM**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **DESCRIPTION** (cont.)

The UC3849 features load share, oscillator synchronization, undervoltage lockout, and programmable output control. Multiple chip operation can be achieved by connecting up to ten UC3849 chips in parallel. The SHARE bus and CLKSYN bus provide load sharing and synchronization to the fastest oscillator respectively. The UC3849 is an ideal controller to achieve high power, secondary side average current mode control.

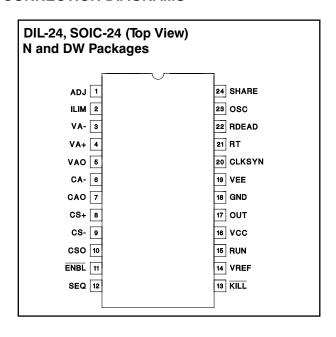

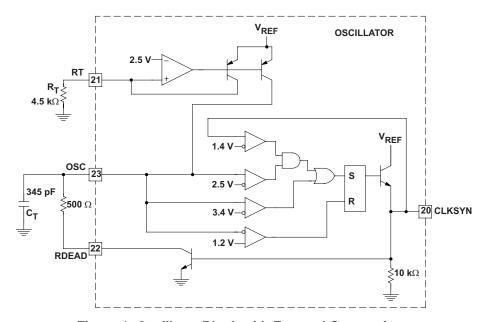

#### **CONNECTION DIAGRAMS**

## ABSOLUTE MAXIMUM RATINGS(1)

|                                                 | VALUE      | UNIT |

|-------------------------------------------------|------------|------|

| Supply Voltage (V <sub>CC</sub> )               | 20         | V    |

| Output current source or sink                   | 0.3        | А    |

| Analog input voltages                           | -0.3 to 7  |      |

| ILIM, KILL, SEQ, ENBL, RUN                      | -0.3 to 7  | V    |

| CLKSYN current source                           | 12         |      |

| RUN current sink                                | 15         | ^    |

| SEQ current sink                                | 20         | mA   |

| RDEAD current sink                              | 20         |      |

| Share bus voltage (voltage with respect to GND) | 0 to 6.2   |      |

| ADJ voltage (voltage with respect to GND)       | 0.9to 6.3  | V    |

| VVEE (voltage with respect to GND)              | -1.5       |      |

| Storage temperaturee                            | -65 to 150 |      |

| Junction temperature                            | -65 to 150 | °C   |

| Lead temperature (soldering, 10 sec.)           | 300        |      |

<sup>(1)</sup> All voltages with respect to VEE except where noted; all currents are positive into, negative out of the specified terminal.

#### RECOMMENDED OPERATING CONDITIONS

|                            | MIN | MAX | UNIT |

|----------------------------|-----|-----|------|

| Input voltage              | 8   | 20  | V    |

| Sink/source output current |     | 250 | mA   |

## RECOMMENDED OPERATING CONDITIONS (continued)

|                       | MIN | MAX  | UNIT |

|-----------------------|-----|------|------|

| Timing resistor (RT)  | 1   | 200  | kΩ   |

| Timing capacitor (CT) | 75  | 2000 | pF   |

## **ELECTRICAL CHARACTERISTICS(1)**

Unless otherwise stated these specifications apply for  $T_A = -40^{\circ}\text{C}$  to 85°C for UC2849; and 0°C to 70°C for UC3849;  $V_{CC} = 12 \text{ V}$ , VEE = GND, Output no load,  $C_T = 345 \text{ pF}$ ,  $RT = 4530\Omega$ ,  $RDEAD = 511\Omega$ ,  $R_{CLKSYN} = 1 \text{ k}\Omega$ ,  $T_A = T_J$ .

| PARAMETER               | TEST CONDITIONS                                                           | MIN | TYP  | MAX | UNIT |

|-------------------------|---------------------------------------------------------------------------|-----|------|-----|------|

| Current Sense Amplifier | ,                                                                         | 1   |      | "   |      |

| Ib                      |                                                                           |     | 0.5  | 3   | μA   |

|                         | T <sub>A</sub> = 25°C                                                     |     |      | 3   | >/   |

| V <sub>IO</sub>         | Over Temperature                                                          |     |      | 5   | mV   |

| Avo                     |                                                                           | 60  | 90   |     | dB   |

| GBW <sup>(2)</sup>      | AcI = 1, $R_{IN}$ = 1 k $\Omega$ , CC = 15 pF, f = 200 kHz <sup>(3)</sup> | 4.5 | 7    |     | MHz  |

| V <sub>OL</sub>         | I <sub>O</sub> = 1 mA, voltage above VEE                                  |     | 0.5  |     |      |

|                         | $I_O = 0 \text{ mA}$                                                      |     | 3.8  |     | V    |

| V <sub>OH</sub>         | $I_O = -1 \text{ mA}$                                                     |     | 3.5  |     |      |

| CMRR                    | -0.2 < Vcm < 6.5 V                                                        |     | 80   |     | i.   |

| PSRR                    | 10 V < VCC < 20 V                                                         |     | 80   |     | dB   |

| Current Error Amplifier | ,                                                                         | 1   | ,    | "   |      |

| lb                      |                                                                           |     | 0.5  | 3   | μA   |

| V <sub>IO</sub>         |                                                                           |     | 3    | 20  | mV   |

| Avo                     |                                                                           | 60  | 90   |     | dB   |

| GBW <sup>(2)</sup>      | AcI = 1, $R_{IN}$ = 1 k $\Omega$ , CC = 15 pF, f = 200 kHz <sup>(3)</sup> | 4.5 | 7    |     | MHz  |

| V <sub>OL</sub>         | I <sub>O</sub> = 1 mA, voltage above VEE                                  |     | 0.5  |     |      |

|                         | $I_O = 0 \text{ mA}$                                                      |     | 3.8  |     | V    |

| V <sub>OH</sub>         | $I_O = -1 \text{ mA}$                                                     |     | 3.5  |     |      |

| CMRR                    | -0.1 < Vcm < 6.5 V                                                        |     | 80   |     | -ID  |

| PSRR                    | 10 V < VCC < 20 V                                                         |     | 80   |     | dB   |

| Voltage Error Amplifier | •                                                                         |     |      |     |      |

| lb                      |                                                                           |     | 0.5  | 3   | μΑ   |

| V <sub>IO</sub>         |                                                                           |     | 2    | 5   | mV   |

| Avo                     |                                                                           | 60  | 90   |     | dB   |

| GBW <sup>(2)</sup>      | f = 200 kHz                                                               | 4.5 | 7    |     | MHz  |

| V <sub>OL</sub>         | $I_O = 175 \mu A$ , voltage above VEE 0.3                                 |     | 0.6  | V   |      |

| V <sub>OH</sub>         | ILIM > 3 V 2.85 3 3.                                                      |     | 3.15 | V   |      |

| V <sub>OH</sub> – ILIM  |                                                                           |     | 100  | mV  |      |

| CMRR                    | -0.1 < Vcm < 6.5 V                                                        |     | 80   |     | AID. |

| PSRR                    | 10 V < VCC < 20 V                                                         |     | 80   |     | dB   |

<sup>(1)</sup> Unless otherwise specified all voltages are with respect to GND. Currents are positive into, negative out of the specified terminal.

<sup>(2)</sup> Ensured by design not 100% tested in production.

<sup>(3)</sup> If a closed loop gain greater than 1 is used, the possible GBW will increase by a factor of ACL + 10; where ACL is the closed loop gain.

## **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise stated these specifications apply for  $T_A = -40^{\circ}C$  to 85°C for UC2849; and 0°C to 70°C for UC3849;  $V_{CC} = 12 \text{ V}$ , VEE = GND, Output no load,  $C_T = 345 \text{ pF}$ , RT = 4530 $\Omega$ , RDEAD = 511 $\Omega$ ,  $R_{CLKSYN} = 1 \text{ k}\Omega$ ,  $T_A = T_J$ .

| PARAMETER                     | TEST CONDITIONS                                                                     | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| 2X Amplifier and Share Amplif | fier                                                                                |      |      |      |      |

| V offset (b; $y = mx + b$ )   |                                                                                     |      |      | 20   | mV   |

| GAIN (m; $y = mx + b$ )       | Slope with AV <sub>OUT</sub> = 1 V and 2 V                                          | 1.98 |      | 2.02 | V    |

| GBW <sup>(2)</sup>            |                                                                                     |      | 100  |      | kHz  |

| R <sub>SHARE</sub>            | VCC = 0, V <sub>SHARE</sub> /I <sub>SHARE</sub>                                     |      | 200  |      | kΩ   |

| Total offset                  | Negative supply is VEE, GND Open, VAO = GND                                         | -75  | 0    | 75   | mV   |

| V <sub>OL</sub>               | VAO = voltage amplifier Vol, volts above VEE                                        | 0.05 | 0.45 | 0.6  |      |

|                               | I <sub>O</sub> = 0 mA, ILIM = 3 V, VAO = voltage amp V <sub>OH</sub>                | 5.7  | 6    | 6.3  | V    |

| V <sub>OH</sub>               | $I_O = -1$ mA, ILIM = 3 V, VAO = voltage amp $V_{OH}$                               | 5.7  | 6    | 6.3  |      |

| Adjust Amplifier              |                                                                                     |      |      | ·    |      |

| V <sub>IO</sub>               |                                                                                     | 40   | 60   | 80   | mV   |

| gm                            | $I_{OUT}$ = -10 $\mu A$ to 10 $\mu A$ , $V_{OUT}$ = 3.5 $V$ , $C_{ADJ}$ = 1 $\mu F$ |      | -1   |      | mS   |

| V                             | I <sub>OUT</sub> = 0                                                                | 0.9  | 1    | 1.1  |      |

| V <sub>OL</sub>               | $I_{OUT} = 50 \mu A$                                                                | 0.85 | 1    | 1.15 | V    |

| V                             | $I_{OUT} = 0$ , $V_{SHARE} = 6.5 V$                                                 | 5.7  | 6    | 6.3  | V    |

| V <sub>OH</sub>               | $I_{OUT} = -50 \mu A$ , $V_{SHARE} = 6.5 V$                                         |      | 6    | 6.3  |      |

| Oscillator                    |                                                                                     |      |      |      |      |

| Frequency                     |                                                                                     | 450  | 500  | 550  | kHz  |

| Max duty cycle                |                                                                                     | 80%  | 85%  | 90%  |      |

| OSC range amplitude           |                                                                                     | 2    | 2.5  | 2.8  | V    |

| Clock Driver/SYNC (CLKSYN)    |                                                                                     |      |      |      |      |

| $V_{OL}$                      |                                                                                     |      | 0.02 | 0.2  |      |

| V                             |                                                                                     |      | 3.6  |      | V    |

| V <sub>OH</sub>               | $R_{CLKSYN} = 200 \Omega$                                                           |      | 3.2  |      |      |

| I <sub>SOURCE</sub>           |                                                                                     |      | 25   |      | mA   |

| R <sub>CLKSYN</sub>           | V <sub>CC</sub> = 0, V <sub>CLKSYN/ICLKSYN</sub>                                    |      | 10   |      | kΩ   |

| V <sub>TH</sub>               |                                                                                     |      | 1.5  |      | V    |

| VREF Comparator               |                                                                                     |      |      |      |      |

| Turn-on threshold             |                                                                                     |      | 4.72 |      | V    |

| Hysteresis                    |                                                                                     |      | 0.4  |      | V    |

## **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise stated these specifications apply for  $T_A = -40^{\circ}C$  to 85°C for UC2849; and 0°C to 70°C for UC3849;  $V_{CC} = 12 \text{ V}$ , VEE = GND, Output no load,  $C_T = 345 \text{ pF}$ , RT = 4530 $\Omega$ , RDEAD = 511 $\Omega$ ,  $R_{CLKSYN} = 1 \text{ k}\Omega$ ,  $T_A = T_J$ .

| PARAMI                | TER                     | TEST CONDITIONS                                                    |     | TYP  | MAX  | UNIT |

|-----------------------|-------------------------|--------------------------------------------------------------------|-----|------|------|------|

| VCC Comparator        | 1                       |                                                                    | - 1 |      |      |      |

| Turn-on thresh        | Turn-on threshold       |                                                                    | 7.9 | 8.3  | 9.5  | V    |

| Hysteresis            |                         |                                                                    |     | 0.4  |      | V    |

| KILL Comparator       |                         |                                                                    | "   | "    | W.   |      |

| Voltage thresh        | old                     |                                                                    |     | 3    |      | V    |

| Sequence Compar       | ator                    |                                                                    | - 1 | "    |      |      |

| Voltage thresh        | old                     |                                                                    |     | 2.5  |      | .,   |

| SEQ SAT               |                         |                                                                    |     | 0.25 |      | V    |

| ENABLE Compara        | or                      |                                                                    |     |      |      |      |

| Voltage thresh        | old                     |                                                                    |     | 2.5  |      | .,   |

| RUN SAT               |                         |                                                                    |     | 0.25 |      | V    |

| Reference             |                         |                                                                    |     |      |      |      |

|                       |                         | $T_A = 25^{\circ}C$ 4.95 5                                         |     | 5    | 5.05 | .,   |

| VREF                  |                         | VCC = 15 V                                                         | 4.9 |      | 5.1  | V    |

| Line regulation       |                         | 10 < VCC < 20                                                      |     | 3    | 15   | .,   |

| Load regulatio        | า                       | 0 < I <sub>O</sub> < 10 mA                                         |     | 3    | 15   | mV   |

| Short circuit I       |                         | VREF = 0 V                                                         | 30  | 60   | 90   | mA   |

| Output Stage          |                         |                                                                    |     |      |      |      |

| Rise time             |                         | C <sub>L</sub> = 100 pF                                            |     | 10   | 20   |      |

| Fall time             |                         | C <sub>L</sub> = 100 pF                                            |     | 10   | 20   | ns   |

| .,                    |                         | VCC > 11 V, I <sub>O</sub> = -10 mA                                | 8.0 | 8.4  | 8.8  |      |

| V <sub>OH</sub>       |                         | $I_{O} = -200 \text{ mA}$                                          | 7.8 |      |      | .,   |

| .,                    |                         | I <sub>O</sub> = 200 mA                                            |     |      | 3.0  | V    |

| V <sub>OL</sub>       | $I_{O} = 10 \text{ mA}$ |                                                                    |     |      | 0.5  |      |

| Virtual Ground        |                         | -                                                                  | I I | I    |      |      |

| V <sub>GND</sub> -VEE |                         | VEE is externally supplied, GND is floating and used as signal GND | 0.2 | 0.75 |      | V    |

| Icc                   | "                       |                                                                    | '   | '    | ,    |      |

| Icc (run)             |                         |                                                                    |     | 21   | 33   | mA   |

#### **Pin Descriptions**

ADJ: The output of the transconductance (gm = -1 ms) amplifier adjusts the control voltage to maintain equal current sharing. The chip sensing the highest output current will have its output clamped to 1 V. A resistor divider between VREF and ADJ drives the control voltage (VA+) for the voltage amplifier. Each slave unit's ADJ voltage increases (to a maximum of 6 V) its control voltage (VA+) until its load current is equal to the master. The 60-mV input offset on the gm amplifier specifies that the unit sensing the highest load current is chosen as the master. The 60-mV offset ensures by design to be greater than the inherent offset of the gm amplifier and the buffer amplifier. While the 60-mV offset represents an error in current sharing, the gain of the current and 2X amplifiers reduces it to only 30 mV. This pin needs a 1-µF capacitor to compensate the amplifier to the master.

**CA-:** The inverting input to the current error amplifier. This amplifier needs a capacitor between CA- and CAO to set its dominant pole.

**CAO:** The output of the current error amplifier which is internally clamped to 4 V. It is internally connected to the inverting input of the PWM comparator.

**CS**–, **CS**+: The inverting and non-inverting inputs to the current sense amplifier. This amplifier is not internally compensated so the user must compensate externally to attain the highest GBW for the application.

**CLKSYN:** The clock and synchronization pin for the oscillator. This is a bidirectional pin that can be used to synchronize several chips to the fastest oscillator. Its input synchronization threshold is 1.4 V. The CLKSYN voltage is 3.6 V when the oscillator capacitor (CT) is being discharged, otherwise it is 0 V. If the recommended synchronization circuit is not used, a 1 k $\Omega$  or lower value resistor from CLKSYN to GND may be needed to increase fall time on CLKSYN pin.

CSO: The output of the current sense amplifier which is internally clamped to 4 V.

**ENBL**: The active low input with a 2.5-V threshold enables the output to switch. SEQ and RUN are driven low when ENBL is above its 2.5-V threshold.

**GND:** The signal ground used for the voltage sense amplifier, current sense amplifier, current error amplifier, voltage reference, 2X amplifier, and share amplifier. The output sink transistor is wired directly to this pin.

KILL: The active low input with a 3.0-V threshold stops the output from switching. Once this function is activated RUN must be cycled low by driving KILL above 3.0 V and either resetting the power to the chip (VCC) or resetting the ENBL signal.

**ILIM:** A voltage on this pin programs the voltage error amplifier's Voh clamp. The voltage error amplifier output represents the average output current. The Voh clamp consequently limits the output current. If ILIM is tied to VREF, it defaults to 3.0 V. A voltage less than 3.0 V connected to ILIM clamps the voltage error amplifier at this voltage and consequently limits the maximum output current.

**OSC:** The oscillator ramp pin which has a capacitor (CT) to ground and a resistor (RDEAD) to the RDEAD pin programs its maximum duty cycle by programming a minimum dead time. The ramp oscillates between 1.2 V to 3.4 V when an RDEAD resistor is used. The maximum duty cycle can be increased by connecting RDEAD to OSC which changes the oscillator ramp to vary between 0.2 V and 3.5 V. In order to ensure zero duty cycle in this configuration VEE should not be connected to GND.

The charge time is approximately  $T_{CHARGE} = R_T \cdot C_T$  when the RDEAD resistor is used.

The dead time is approximately T<sub>DISCHARGE</sub> = 2 • RDEAD • C<sub>T</sub>.

Frequency

$$\approx \frac{1}{T_{CHARGE} + T_{DISCHARGE}}$$

(1)

Maximum Duty Cycle

$$\approx \frac{T_{CHARGE}}{T_{CHARGE} + T_{DISCHARGE}}$$

(2)

The  $C_T$  capacitance should be increased by approximately 40 pF to account for parasitic capacitance.

**OUT:** The output of the PWM driver. It has an upper clamp of 8.5 V. The peak current sink and source are 250 mA. All UVLO, SEQ, ENBL, and KILL logic either enable or disable the output driver.

**RDEAD:** The pin that programs the maximum duty cycle by connecting a resistor between it and OSC. The maximum duty cycle is decreased by increasing this resistor value which increases the discharge time. The dead time, the time when the output is low, is  $2 \bullet RDEAD \bullet C_T$ . The  $C_T$  capacitance should be increased by approximately 40 pF to account for parasitic capacitance.

RT: This pin programs the charge time of the oscillator ramp. The charge current is

$$\frac{\text{VREF}}{2 \times R_{\mathsf{T}}} \tag{3}$$

The charge time is approximately  $T_{CHARGE} \approx R_T \bullet C_T$  when the RDEAD resistor is used.

The dead time is approximately  $T_{DISCHARGE} \approx 2 \bullet RDEAD \bullet C_T$ .

**RUN:** This is an open collector logic output that signifies when the chip is operational. RUN is pulled high to VREF through an external resistor when VCC is greater than 8.4 V, VREF is greater than 4.65 V, SEQ is greater than 2.5 V, and KILL lower than 3.0 V. RUN connected to the VA+ pin and to a capacitor to ground adds an RC rise time on the VA+ pin initiating a soft start.

**SEQ:** The sequence pin allows the sequencing of startup for multiple units. A resistor between VREF and SEQ and a capacitor between SEQ and GND creates a unique RC rise time for each unit which sequences the output startup.

SHARE: The nearly dc voltage representing the average output current. This pin is wired directly to all SHARE pins and is the load share bus.

VA+, VA-: The inverting and non-inverting inputs to the voltage error amplifier.

**VAO:** The output of the voltage error amplifier. Its Voh is clamped with the ILIM pin.

VCC: The input voltage of the chip. The chip is operational between 8.4 V and 20 V.

**VEE:** The negative supply to the chip which powers the lower voltage rail for all amplifiers. The chip is operational if VEE is connected to GND or if GND is floating. When voltage is applied externally to VEE, GND becomes a virtual ground because of an internal diode between VEE and GND. The GND current flows through the forward biased diode and out VEE. GND is always the signal ground from which the voltage reference and all amplifier inputs are referenced.

**VREF:** The reference voltage equal to 5.0 V.

## **Circuit Block Description**

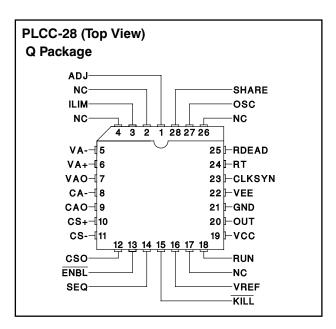

## **PWM Oscillator**

The oscillator block diagram with external connections is shown in Figure 1. A resistor ( $R_T$ ) connected to pin RT sets the linear charge current;

$$I_{RT} \approx \frac{2.5 \text{ V}}{R_T}$$

Figure 1. Oscillator Block with External Connections

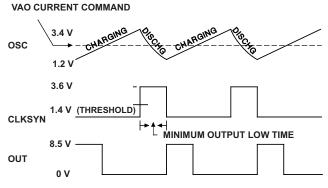

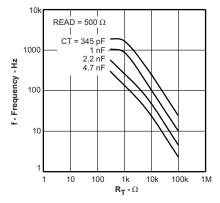

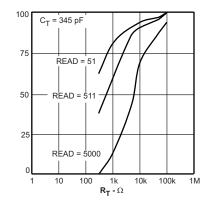

The timing capacitor  $(C_T)$  is linearly charged with the charge current forcing the OSC pin to charge to a 3.4-V threshold. After exceeding this threshold, the RS flip-flop is set driving CLKSYN high and RDEAD low which discharges  $C_T$ . This discharge time with the RC time delay of  $2 \cdot C_T \cdot RDEAD$  is the minimum output low time. OSC continues to discharge until it reaches a 1.2 -V threshold and resets the RS flip-flop which repeats the charging sequence as shown in Figure 2. Equations to approximate frequency and maximum duty cycle are listed under the OSC pin description. Figure 3 and Figure 4 graphs show measured variation of frequency and maximum duty cycle with varying RT, CT, and RDEAD component values.

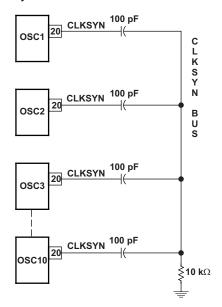

As shown in Figure 5, several oscillators are synchronized to the highest free running frequency by connecting 100-pF capacitors in series with each CLKSYN pin and connecting the other side of the capacitors together forming the CLKSYN bus. The CLKSYN bus is then pulled down to ground with a resistance of approximately 10  $k\Omega$ . Referring to Figure 1, the synchronization threshold is 1.4 V. The oscillator blanks any synchronization pulse that occurs when OSC is below 2.5 V. This allows units, once they discharge below 2.5 V, to continue through the current discharge and subsequent charge cycles whether or not other units on the CLKSYN bus are still synchronizing. This requires the frequency of all free running oscillators to be within 40% of each other to assure synchronization.

Figure 2. Oscillator and PWM Output Waveform

Figure 3. Output Frequency

Figure 4. Maximum Duty Cycle

#### **Grounds, Voltage Sensing and Current Sensing**

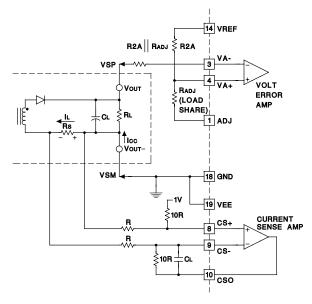

The voltage is sensed directly at the load. Proper load sharing requires the same sensed voltage for each power supply connected in parallel. Referring to Figure 6, the positive sense voltage (VSP) connects to the voltage error amplifier inverting terminal (VA-), the return lead for the on-chip reference is used as the negative sense (VSM). The current is sensed across the shunt resistor,  $R_S$ .

Figure 6 shows one recommended voltage and current sensing scheme when VEE is connected to GND. The signal ground is the negative sense point for the output voltage and the positive sense point for the output current. The voltage offset on the current sense amplifier is not needed if VEE is separated from GND. VEE is the negative supply for the current sense amplifier. When it is separated from GND, it extends the current sense amplifier's common mode input voltage range to include VEE which is approximately -0.7 V below ground. The resistor  $R_{ADJ}$  is used for load sharing. The unit which is the master will force  $V_{ADJ}$  to 1.0 V. Therefore, the regulated voltage being sensed is actually:

Figure 5. Oscillator Synchronization Connection Diagram

Figure 6. Voltage and Current Sense VEE Tied to GND

$$VSP - VSM = \left(VREF - V_{ADJ}\right) \times \left(\frac{R_{ADJ}}{R1 + R_{ADJ}}\right) + V_{ADJ}$$

(4)

$$VSM = 0 V$$

,  $V_{ADJ} = 1 V(master)$ ,  $VREF = 5 V$  (5)

$$VSP = 4 \times \left(\frac{R_{ADJ}}{R1 + R_{ADJ}}\right) + 1 V$$

(6)

The ADJ pin voltage on the slave chips will increase forcing their load currents to increase to match the master.

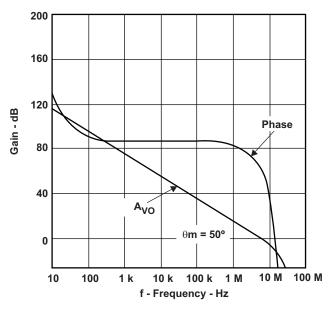

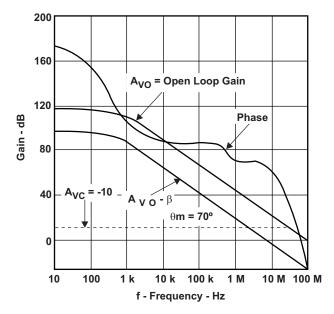

The ac frequency response of the voltage error amplifier is shown in Figure 7.

Figure 7. AC Frequency Response of the Voltage Error Amplifier

#### Startup and Shutdown

Isolated power up can be accomplished using the UCC1889. Application Note U-149 is available for additional information.

The UC3849 offers several features that enhance startup and shutdown. Soft start is accomplished by connecting RUN to VA+ and a capacitor to ground. The resulting RC rise time on the VA+ pin initiates a soft start. It can also be accomplished by connecting RUN to ILIM. When RUN is low it commands zero load current, assuring a soft start. The undervoltage lockout (UVLO) is a logical AND of ENBL < 2.5 V, SEQ > 2.5 V, VCC > 8.4 V and VREF > 4.65 V. The block diagram shows that the thresholds are set by comparators. By placing an RC divider on the SEQ pin, the enabling of multiple chips can be sequenced with different RC time constants. Similarly, different RC time constants on the ENBL pins can sequence shutdown. The UVLO keeps the output from switching; however the internal reference starts up with VCC less than 8.4 V. The KILL input shuts down the switching of the chip. This can be used in conjunction with an overvoltage comparator for overvoltage protection. In order to restart the chip after KILL has been initiated, the chip must be powered down and then back up. A pulse on the ENBL pin also accomplishes this without actually removing voltage to the VCC pin.

#### Load Sharing

Load sharing is accomplished similar to the UC1907. The sensed current for the UC3849 has an ac component that is amplified and then averaged. The voltage error amplifier output is the current command signal representing the average output load current. The ILIM pin programs the upper clamp voltage of this amplifier and consequently the maximum load current. A gain of 2 amplifier connected between the voltage error amplifier output and the share amplifier input increases the current share resolution and noise margin. The average current is used as an input to a source only load share buffer amplifier. The output of this amplifier is the current share bus. The device with the highest sensed current will have the highest voltage on the current share bus and consequently act as the master. The 60-mV input offset ensures that the unit sensing the highest load current is chosen as the master.

The adjust amplifier is used by the remaining (slave) devices to adjust their respective references high in order to balance each device's load current. The master's ADJ pin will be at its 1.0-V clamp and connected back to the non-inverting voltage error amplifier input through a high value resistor. This requires the user to initially calculate the control voltage with the ADJ pin at 1.0 V.

VREF can be adjusted 150 mV to 300 mV which compensates for 5% unit to unit reference mismatch and external resistor mismatch.  $R_{ADJ}$  typically is 10 to 30 times larger than R1. This also attenuates the overall variation of the ADJ clamp of 1 V  $\pm$ 100 mV by a factor of 10 to 30, contributing only a 3 mV to 10 mV additional delta to VREF. Refer to the UC3907 Application Note U-130 for further information on parallel power supply load sharing.

#### **Current Control Loop**

The current sense amplifier (CSA) is designed specifically for the task of sensing and amplifying the inductor ripple current at frequencies up to 1 MHz. The CSA's input offset voltage (VIO) is trimmed to less than 1 mV to minimize error of the average current signal. This amplifier is not internally compensated allowing the user to optimally choose the zero crossing bandwidth.on on parallel power supply load sharing.

Frequency(0 dB) =

$$\frac{1}{2\pi R_{INV} \times C_{COMP}}$$

(7)

$R_{INV}$  is the input resistance at the inverting terminal CS-  $C_{COMP}$  is the capacitance between  $C_{S}$ - and CSO.

Although it is only unity gain stable for a GBW of 7 MHz, the amplifier is typically configured with a differential gain of at least 10, allowing the amplifier to operate at 70 MHz with sufficient phase margin. A closed loop gain of 10 attenuates the output by 20.8 dB to the inverting terminal assuring stability. The amplifier's gain fed back into the inverting terminal is less than unity at 7 MHz, where the phase margin begins to roll off. See Figure 8 for typical Bode plot.

$$20.8 = 20 \log \times \frac{1}{11} \tag{8}$$

Figure 8. Current Sense Amplifier and Curent Error Amplifier Bode Plot

The gain of the differential current sense amplifier ( $CS_{GAIN}$ ) is calculated by knowing the maximum load current. The maximum voltage across the shunt resistor ( $R_S$ ) divided by  $R_S$  is the maximum load current. By amplifying the voltage across RS,  $V_{RS}$ , to be equal to the voltage error amplifier Voh, the current control loop keeps the load from exceeding its current limit. Voh is set at 3.0 V if ILIM is connected to VREF. The maximum current limit clamp can be reduced by reducing the voltage at ILIM to less than 3.0 V as described in the ILIM pin description.

$$R_{S} = \frac{V_{RS}}{\text{Max I}_{\text{LOAD}}}$$

(9)

$$CS_{GAIN} = \frac{V_{ILIM}}{V_{RS}}$$

(10)

The current error amplifier (CEA) also needs its loop compensated by the user with the same criteria as the current sense amplifier. This amplifier is essentially the same wide bandwidth amplifier without the input offset voltage trim. The zero crossing can also be approximately calculated with Equation 7. The gain bandwidth of the current loop is optimized by matching the inductor downslope  $(V_O/L)$  to the oscillator ramp slope  $(V_S \bullet f_S)$ . Subharmonic oscillation problems are avoided by keeping the amplified inductor downslope less than the oscillator ramp slope.

The following equation determines the current error amplifier gain (GCA):

$$GCA = \frac{V_S \times f_S}{\left(V_{O/L}\right) \times R_S \times CS_{GAIN}};$$

(11)

where CS<sub>GAIN</sub> and R<sub>S</sub> are defined by Equation 9 and Equation 10,

Vs is the oscillator peak to peak voltage,

fs is the oscillator frequency,

Vo is the output voltage,

and L is the inductance.

Additional Information about average current mode control can be found in Unitrode Application Note U-140.

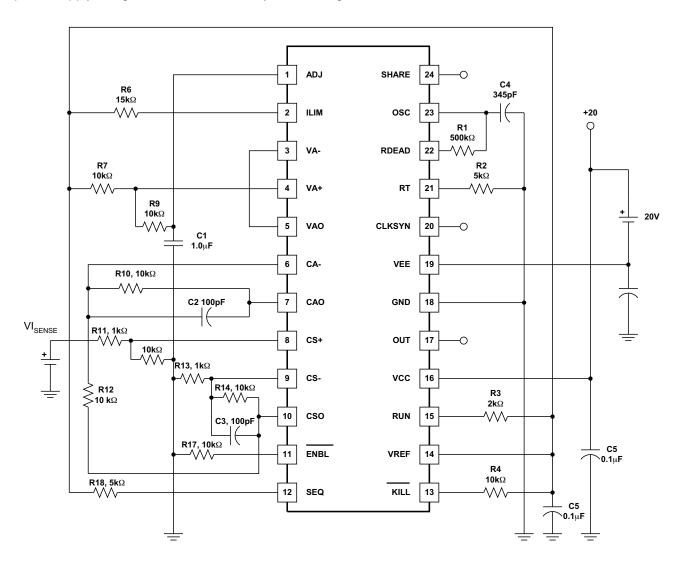

## **Design Example**

Figure 9 is an open loop test that lets the user test the circuit blocks discussed without having to build an entire control loop. The pulse width can be varied by either the  $V_{ADJ}$  or the  $VI_{SENSE}$  inputs. Figure 10 shows an isolated power supply using the UC3849 secondary side average current mode controller.

Figure 9. Open Loop Circuit

Figure 10. UC3849 Application Diagram

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| UC2849DW         | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | Cu NiPdAu        | Level-2-260C-1 YEAR          |

| UC2849DWG4       | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | Cu NiPdAu        | Level-2-260C-1 YEAR          |

| UC2849N          | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC2849NG4        | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3849DW         | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | Cu NiPdAu        | Level-2-260C-1 YEAR          |

| UC3849DWG4       | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | Cu NiPdAu        | Level-2-260C-1 YEAR          |

| UC3849DWTR       | ACTIVE                | SOIC            | DW                 | 24   | 2000           | Green (RoHS & no Sb/Br)   | Cu NiPdAu        | Level-2-260C-1 YEAR          |

| UC3849DWTRG4     | ACTIVE                | SOIC            | DW                 | 24   | 2000           | Green (RoHS & no Sb/Br)   | Cu NiPdAu        | Level-2-260C-1 YEAR          |

| UC3849Q          | ACTIVE                | PLCC            | FN                 | 28   | 37             | TBD                       | Cu NiPdAu        | Level-2-220C-1 YEAR          |

| UC3849QTR        | ACTIVE                | PLCC            | FN                 | 28   | 750            | TBD                       | Cu NiPdAu        | Level-2-220C-1 YEAR          |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC3849:

## **PACKAGE OPTION ADDENDUM**

4-Nov-2008

Military: UC1849

NOTE: Qualified Version Definitions:

• Military - QML certified for Military and Defense Applications

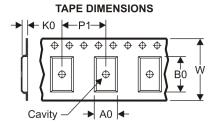

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| UC3849DWTR | SOIC            | DW                 | 24 | 2000 | 330.0                    | 24.4                     | 10.85   | 15.8    | 2.7     | 12.0       | 24.0      | Q1               |

| UC3849QTR  | PLCC            | FN                 | 28 | 750  | 330.0                    | 24.4                     | 12.95   | 12.95   | 5.0     | 16.0       | 24.0      | Q1               |

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC3849DWTR | SOIC         | DW              | 24   | 2000 | 346.0       | 346.0      | 41.0        |

| UC3849QTR  | PLCC         | FN              | 28   | 750  | 346.0       | 346.0      | 41.0        |

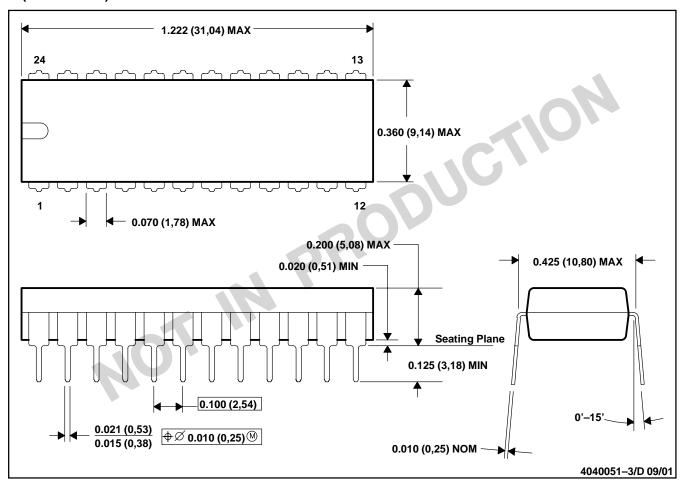

## N (R-PDIP-T24)

#### PLASTIC DUAL-IN-LINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-010

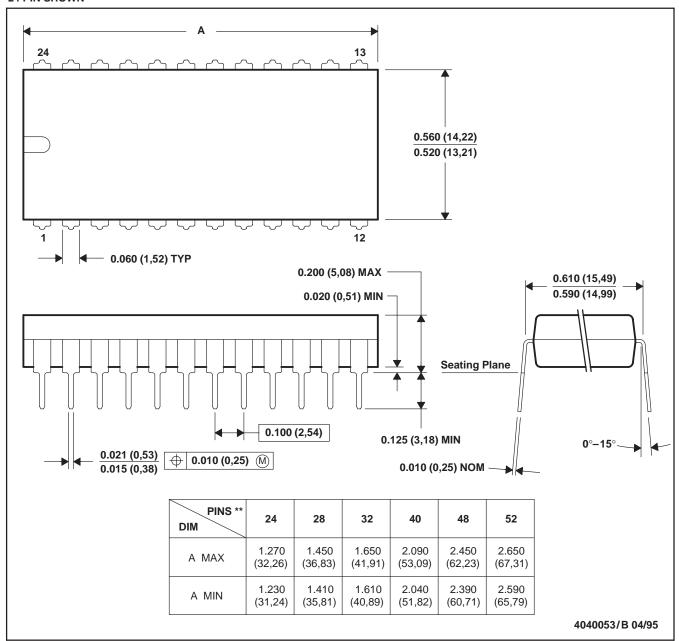

## N (R-PDIP-T\*\*)

#### PLASTIC DUAL-IN-LINE PACKAGE

#### 24 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-011

- D. Falls within JEDEC MS-015 (32 pin only)

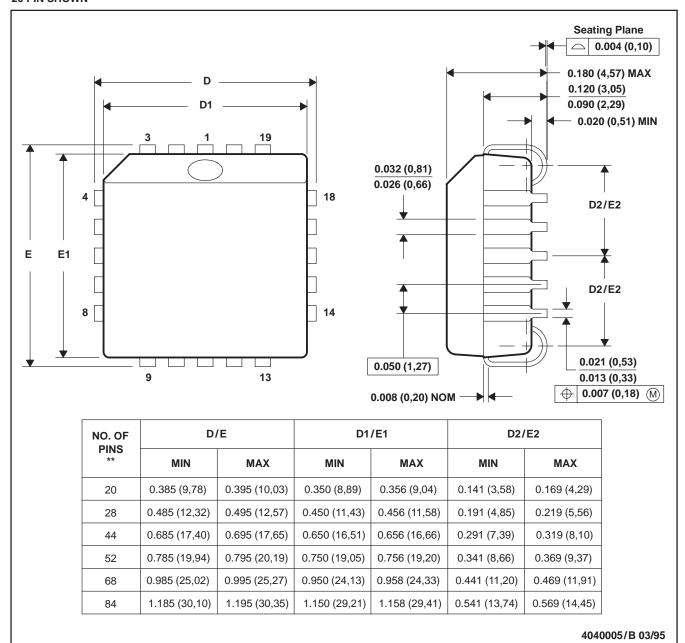

#### FN (S-PQCC-J\*\*)

#### 20 PIN SHOWN

#### PLASTIC J-LEADED CHIP CARRIER

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-018

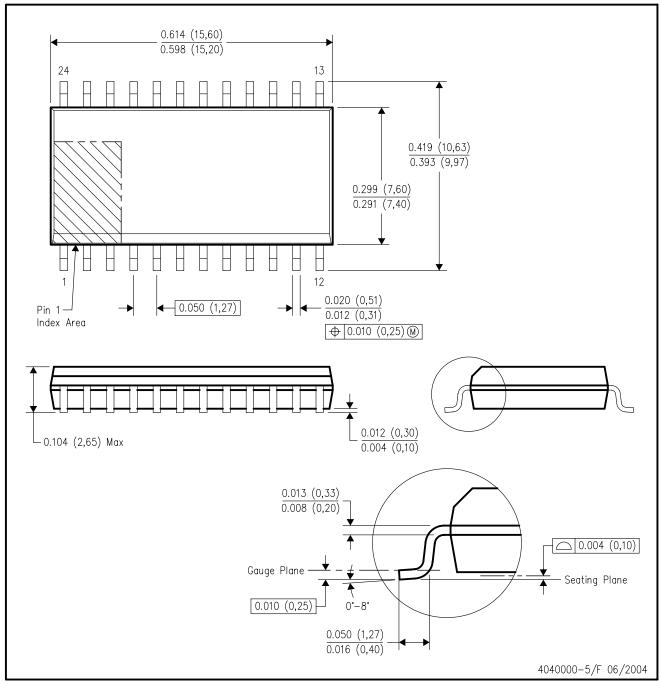

# DW (R-PDSO-G24)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AD.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated